- 您现在的位置:买卖IC网 > Sheet目录319 > CK-S6-SP623-G (Xilinx Inc)BOARD DEV S6 WITH TX

Chapter 1: SP623 Board Features and Operation

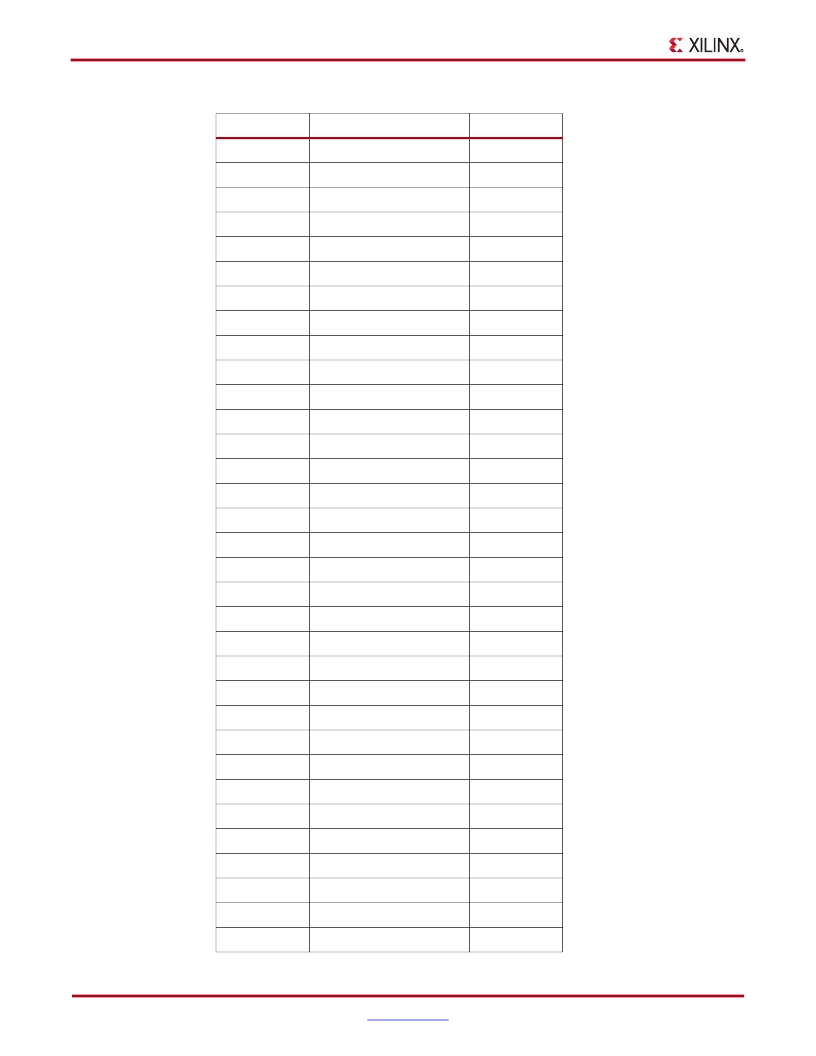

Table 1-18:

Vita 57.1 FMC2 HPC Connections at J113 (Cont’d)

FPGA Pin

AE1

AA2

AA1

Y3

Y1

W2

W1

R10

T9

P3

P1

N6

P6

P5

R5

N8

N7

R4

R3

R9

P8

N5

N4

P10

N9

M10

M9

Y6

Y5

Net Name

FMC2_HA09_N

FMC2_HA10_P

FMC2_HA10_N

FMC2_HA11_P

FMC2_HA11_N

FMC2_HA12_P

FMC2_HA12_N

FMC2_HA13_P

FMC2_HA13_N

FMC2_HA14_P

FMC2_HA14_N

FMC2_HA15_P

FMC2_HA15_N

FMC2_HA16_P

FMC2_HA16_N

FMC2_HA17_CC_P

FMC2_HA17_CC_N

FMC2_HA18_P

FMC2_HA18_N

FMC2_HA19_P

FMC2_HA19_N

FMC2_HA20_P

FMC2_HA20_N

FMC2_HA21_P

FMC2_HA21_N

FMC2_HA22_P

FMC2_HA22_N

FMC2_HA23_P

FMC2_HA23_N

FMC Pin

E10

K13

K14

J12

J13

F13

F14

E12

E13

J15

J16

F16

F17

E15

E16

K16

K17

J18

J19

F19

F20

E18

E19

K19

K20

J21

J22

K22

K23

U14.13

FMC2_I2C_SCL

C30

30

U14.12

AB14

AC14

FMC2_I2C_SDA (1)

FMC2_LA00_CC_P

FMC2_LA00_CC_N

C31

G6

G7

SP623 Board User Guide

UG751 (v1.1) September 15, 2010

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

CK-V6-ML628-G

KIT VIRTEX-6 CHAR ML628

CLSD004

LED DRIVER PROGRAMMER W/CABLE

CMC484812

RACK STEEL 12X48X48 GRY

CMCQP3

PANEL INNER 25.59X15" GREY

CML12C32SLK

KIT STUDENT LEARNING 16BIT HCS12

CMR-8040

RACK CABLE MANAGMNT OPEN ASSMBLY

COP8SG-EPU

BOARD PROTOTYPE/TARGET COP8

CORE1553-DEV-KIT

KIT DEVELOPMENT FOR IP CORE1553

相关代理商/技术参数

CK-S6-SP623-G-J

功能描述:BOARD DEV S6 WITH TX RoHS:是 类别:编程器,开发系统 >> 通用嵌入式开发板和套件(MCU、DSP、FPGA、CPLD等) 系列:Spartan® 6 LXT 标准包装:1 系列:PICDEM™ 类型:MCU 适用于相关产品:PIC10F206,PIC16F690,PIC16F819 所含物品:板,线缆,元件,CD,PICkit 编程器 产品目录页面:659 (CN2011-ZH PDF)

CKS-820

制造商:Sunhayato 功能描述: 制造商:Sunhayato 功能描述:PCB DOUBLE SIDED PROTOTYPING F

CKS-CCEA50OO

制造商:Lorlin Electronics Ltd 功能描述:

CKSF03

制造商:ILME 功能描述:INSERT FEMALE 26-14 AWG 3P+E 制造商:ILME 功能描述:INSERT, FEMALE, 26-14 AWG, 3P+E 制造商:ILME 功能描述:INSERT, FEMALE, 26-14 AWG, 3P+E, Series:CKS, No. of Contacts:3, No. of Rows:2, G

CKSF04

制造商:ILME 功能描述:INSERT FEMALE 26-14 AWG 4P+E 制造商:ILME 功能描述:INSERT, FEMALE, 26-14 AWG, 4P+E 制造商:ILME 功能描述:INSERT, FEMALE, 26-14 AWG, 4P+E, Series:CKS, No. of Contacts:4, No. of Rows:2, G

CKSM03

制造商:ILME 功能描述:INSERT MALE 26-14 AWG 3P+E 制造商:ILME 功能描述:INSERT, MALE, 26-14 AWG, 3P+E 制造商:ILME 功能描述:INSERT, MALE, 26-14 AWG, 3P+E, Series:CKS, No. of Contacts:3, No. of Rows:2, Gen

CKSM04

制造商:ILME 功能描述:INSERT MALE 26-14 AWG 4P+E 制造商:ILME 功能描述:INSERT, MALE, 26-14 AWG, 4P+E 制造商:ILME 功能描述:INSERT, MALE, 26-14 AWG, 4P+E, Series:CKS, No. of Contacts:4, No. of Rows:2, Gen

CK-SPACER

制造商:Thomas & Betts 功能描述: